ウィンボンド・エレクトロニクスはUCIeコンソーシアムへ参加したことを発表。

このオープン規格は、1つのパッケージ内における複数チップレットを相互接続するための通信方式を定義し、オープンなチップレットエコシステムを実現、高度な2.5D/3Dデバイスの開発を容易にしてくれます。

ウィンボンド・エレクトロニクス UCIeコンソーシアムへ参加

高性能メモリ ICのリーディングカンパニーである「ウィンボンド・エレクトロニクス」

2.5D/3D実装の最終歩留まり向上に不可欠なKGDを供給するサプライヤーとして定評があります。

そんな「ウィンボンド・エレクトロニクス」はUCIeコンソーシアムへ参加したことを発表。

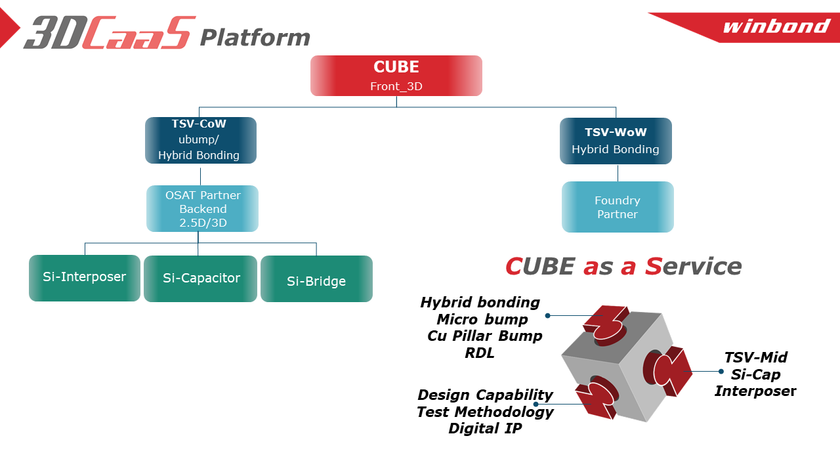

SoC設計の簡素化と、2.5D/3D BEOL実装を容易にするインターコネクトの標準化を支援。

UCIe 1.0仕様は、高帯域幅のインターフェイスを実現する完全に標準化されたダイ間インターコネクトを提供し、低レイテンシ、低消費電力、および高性能なSoCとメモリのインターコネクトを実現。

最終的には、標準化によって、デバイスメーカーとエンドユーザーに高い価値を提供する高性能製品の導入が加速され、先進的なマルチチップエンジンの市場成長が促進されるように活動されます。

1つのパッケージ内における複数チップレットを相互接続するための通信方式を定義し、オープンなチップレットエコシステムを実現、高度な2.5D/3Dデバイスの開発を容易に。

ウィンボンド・エレクトロニクスにて発表された、UCIeコンソーシアムへの参加の紹介でした。